Field-Programmable Gate Array-Based Software-Defined Radio

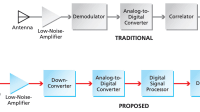

This technology helps mitigate the restrictions imposed on FPGA-based designs by external input-output (IO) bandwidth mismatch.

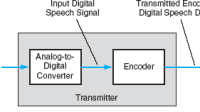

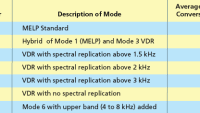

There are existing wideband communications systems that were built using field-programmable gate array (FPGA)-based software-defined radio (SDR) designs. Despite the inherent advantages of these systems, some are functionally restricted by limited output bandwidth. An FPGA-based SDR was designed that can compress sampled intermediate-frequency (IF) signals. The compression scheme used in the final design is based on flexible operator-defined, time-frequency bins and independent energy thresholds for each bin.

The FPGA-based SDR can compress sampled wideband IF signals based on reprogrammable parameters. The design was developed around the concept of independent, operator-defined time-frequency bins and evaluation of the energy in each bin. Although the design concept incorporated bins with varying time-window periods, the final design was simplified so that each bin used the same period.

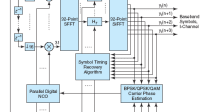

Xilinx’s System Generator software was utilized to develop and test the behavioral definition of the design. The tool was also used to synthesize the design, perform the place-and-route functions, and generate the .bin file that provides the FPGA’s configuration information. The development tool provided a layer of abstraction that reduced the requirement for in-depth knowledge with respect to HDL coding. If the design required management of internal hardware clocks, then the ability to code in an HDL would have been more critical.

The SDR was developed for a Virtex-4 FPGA architecture. While this can potentially affect its portability, the SysGen FFT v4.1 module was the only component used that is not backward-compatible to the Virtex-1.

Two versions of the algorithm were built and tested. The first utilized an 8-point FFT, which simplified analysis efforts. The second version utilized a 1024-point FFT and helped verify the requirements for scaling the design. Both versions were tested using single- and multi-frequency input signals, without restrictions on the output memory. This ensured the basic compression scheme operated properly. Then, the 1,024-point algorithm was used to verify the design and automatically adjust its operations based on the available storage capacity. Testing provided insights regarding the effects and workarounds for machine epsilon. It also verified the design’s desired functional operations.

Although the final design operated as expected, it has performance limitations that should be recognized and considered. All of the development tests were conducted such that the digital input frequencies and the defined bin frequencies were an exact match. If frequencies that did not match the FFT window, i.e., frequencies that did not have an integer number of cycles per FFT window, were used, there would be a slight smearing effect in the frequency domain. It is assumed that this effect is minor, and would not significantly impact the efficacy of the algorithm. The tests also assumed the input signal and the SDR shared the same sample frequency. If this were not the case, the implementation could correct for this with interpolation or decimation, or similar multi-rate signal processing.

This work was done by Durke A. Wright of the U.S. Navy. For more information, download the Technical Support Package (free white paper) at www.defensetechbriefs.com/tsp under the Electronics/Computers category. NRL-0039

This Brief includes a Technical Support Package (TSP).

Field-Programmable Gate Array-Based Software-Defined Radio

(reference NRL-0039) is currently available for download from the TSP library.

Don't have an account?

Overview

The document is a Master's thesis titled "Field Programmable Gate Array (FPGA) Based Software Defined Radio (SDR) Design," authored by Durke Wright and submitted to the Naval Postgraduate School in March 2009. The thesis explores the design and implementation of a Software Defined Radio (SDR) using Field Programmable Gate Array (FPGA) technology, addressing the limitations of traditional communication systems.

The primary focus of the research is on enhancing the capabilities of wideband communication systems, which often suffer from restricted output bandwidth. The author identifies the need for more flexible and efficient communication solutions, particularly in military and defense applications where adaptability and performance are critical. The thesis proposes a novel approach that leverages the reconfigurability of FPGAs to implement advanced signal processing techniques.

One of the key contributions of the thesis is the development of a compression scheme for sampled intermediate frequency signals. This scheme aims to optimize the use of bandwidth while maintaining signal integrity and quality. By utilizing FPGA technology, the design allows for real-time processing and adaptability to various communication standards and protocols, making it a versatile solution for modern communication challenges.

The document outlines the methodology used in the design process, including the selection of hardware components, software tools, and the overall architecture of the SDR system. It also discusses the testing and validation of the proposed design, providing insights into its performance metrics and potential applications.

In addition to the technical aspects, the thesis reflects on the implications of SDR technology in the context of military operations, emphasizing the importance of rapid deployment and reconfiguration in dynamic environments. The author concludes that FPGA-based SDRs represent a significant advancement in communication technology, offering enhanced flexibility, efficiency, and performance.

Overall, this thesis contributes to the field of communication systems by presenting a comprehensive study of FPGA-based SDR design, highlighting its potential to revolutionize how information is transmitted and processed in various applications. The work serves as a valuable resource for researchers and practitioners interested in the intersection of FPGA technology and software-defined radio systems.

Top Stories

INSIDERDesign

![]() How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

NewsSensors/Data Acquisition

![]() Microvision Aquires Luminar, Plans Relationship Restoration, Multi-industry Push

Microvision Aquires Luminar, Plans Relationship Restoration, Multi-industry Push

INSIDERManned Systems

![]() A Next Generation Helmet System for Navy Pilots

A Next Generation Helmet System for Navy Pilots

NewsAR/AI

![]() Accelerating Down the Road to Autonomy

Accelerating Down the Road to Autonomy

INSIDERDefense

![]() New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

ArticlesAR/AI

![]() CES 2026: Bosch is Ready to Bring AI to Your (Likely ICE-powered) Vehicle

CES 2026: Bosch is Ready to Bring AI to Your (Likely ICE-powered) Vehicle

Webcasts

Semiconductors & ICs

![]() Advantages of Smart Power Distribution Unit Design for Automotive...

Advantages of Smart Power Distribution Unit Design for Automotive...

Unmanned Systems

![]() Quiet, Please: NVH Improvement Opportunities in the Early Design...

Quiet, Please: NVH Improvement Opportunities in the Early Design...

Electronics & Computers

![]() Cooling a New Generation of Aerospace and Defense Embedded...

Cooling a New Generation of Aerospace and Defense Embedded...

Automotive

![]() Battery Abuse Testing: Pushing to Failure

Battery Abuse Testing: Pushing to Failure

Transportation

![]() A FREE Two-Day Event Dedicated to Connected Mobility

A FREE Two-Day Event Dedicated to Connected Mobility