Asymmetric Core Computing for High-Performance Applications

Methodologies and performance data were assessed relating to high-performance computing technologies for the warfighter.

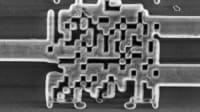

High-performance computing (HPC) users have traditionally relied upon two things to supply them with processing power: speed of the central processing units (CPUs) and the scalability of the system. There are problems with this approach. Physical limitations are curtailing clock speed increases in general-purpose CPUs, the von Neumann load-execute-store approach does not map well to every computational problem, and systems of thousands of processors might be very inefficient, depending upon processor interconnection limitations. Blending asymmetric computing resources makes sense for addressing the needs relating to the U.S. Army HPC perspective. Several versatile, commodity-based options are coming online that now include throughput architectures such as graphics processing units (GPUs), reconfigurable systems built on field-programmable gate arrays (FPGAs), multi- and many-core x86-based systems, and heterogeneous systems such as the Cell processor (incorporating a standard CPU and vector processing unit). These options allow for smaller footprint systems with tremendous speed-ups compared to traditionally large clusters of von Neumann general-purpose CPUs.

The goal is to combine the asymmetric capabilities of these various cores into a complete, high-performance computing system. The primary focus is on battlespace applications to move HPC closer to the soldier and the field commander. Doing so opens up new possibilities to increase the capabilities of the soldier, and the systems being used in many application areas (e.g. sensors and intelligence applications). Algorithm development for applications needing improvements in speed and/or fidelity will be critical.

Each of these may be used to provide performance that, at one time, was only available by using Application Specific Integrated Circuits (ASICs) or large-scale, fixed HPC assets. Newer methodologies hold the hope of being more cost efficient and deployable, along with providing faster development times and allowing the use of algorithms that remain modifiable at all stages of development and fielding.

There is a fundamental change occurring in the HPC field as throughput architectures gain in importance, market share, and raw floating-point computational capacity. Portable, and even handheld high-performance computers, are quickly becoming a reality, and a concerted effort is needed to make these technologies viable for Army forces. New approaches are holding promise for moving these technologies more into the open-source arena, thus allowing researchers more direct understanding and control at low levels. These efforts should greatly facilitate the maturation of compiler and API technologies.

This work was done by Dale Shires, Song Jun Park, Brian Henz, Jerry Clarke, Lam Nguyen, and Kelly Kirk of the Army Research Laboratory. For more information, download the Technical Support Package (free white paper) at www.defensetechbriefs.com/tsp under the Electronics/Computers category. ARL-0086

This Brief includes a Technical Support Package (TSP).

Asymmetric Core Computing for High-Performance Applications

(reference ARL-0086) is currently available for download from the TSP library.

Don't have an account?

Overview

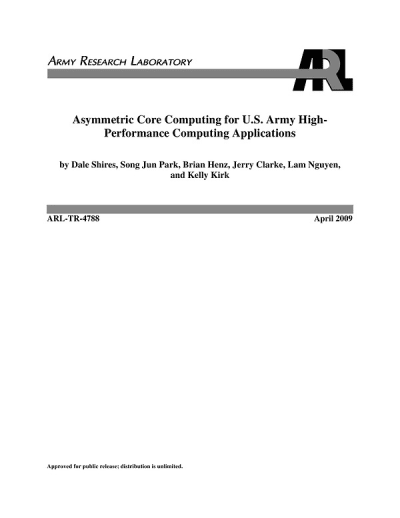

The report titled "Asymmetric Core Computing for U.S. Army High-Performance Computing Applications" discusses the evolving landscape of high-performance computing (HPC) and its implications for the U.S. Army. Authored by Dale Shires and colleagues, the document highlights the limitations of traditional HPC approaches, which have primarily relied on the speed of central processing units (CPUs) and system scalability. As physical constraints hinder clock speed increases in general-purpose CPUs, the report emphasizes the need for alternative computing architectures.

The authors explore various emerging technologies that can enhance HPC capabilities, including graphics processing units (GPUs), field programmable gate arrays (FPGAs), multi-core x86 systems, and heterogeneous systems like the Cell processor. These technologies offer versatile, commodity-based solutions that can address the inefficiencies associated with traditional HPC systems, particularly in terms of processor interconnection limitations and the von Neumann architecture's constraints.

The report outlines the potential of these asymmetric computing resources to deliver performance levels previously achievable only through application-specific integrated circuits (ASICs) or large-scale fixed HPC assets. By leveraging these newer methodologies, the Army can achieve greater cost efficiency, faster deployment, and more flexible algorithm development throughout the lifecycle of HPC technologies.

Key sections of the report delve into specific technologies, including the Cell processor, FPGAs, and GPUs, with detailed discussions on their applications in various computational problems. For instance, the report examines the use of GPUs in N-body simulations and Monte Carlo methods, as well as their role in obstacle detection and avoidance tasks. These examples illustrate how asymmetric computing can be effectively integrated into military applications, enhancing the capabilities of the U.S. Army warfighter.

The report concludes by emphasizing the importance of adapting to these emerging computing paradigms to maintain a competitive edge in military operations. It advocates for continued research and development in asymmetric core computing to fully exploit the potential of these technologies in supporting the Army's high-performance computing needs.

Overall, the document serves as a comprehensive overview of the current state of HPC, the challenges faced, and the promising directions for future research and application in the context of the U.S. Army.

Top Stories

INSIDERDesign

![]() How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

NewsSensors/Data Acquisition

![]() Microvision Aquires Luminar, Plans Relationship Restoration, Multi-industry Push

Microvision Aquires Luminar, Plans Relationship Restoration, Multi-industry Push

INSIDERManned Systems

![]() A Next Generation Helmet System for Navy Pilots

A Next Generation Helmet System for Navy Pilots

NewsAR/AI

![]() Accelerating Down the Road to Autonomy

Accelerating Down the Road to Autonomy

INSIDERDefense

![]() New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

ArticlesAR/AI

![]() CES 2026: Bosch is Ready to Bring AI to Your (Likely ICE-powered) Vehicle

CES 2026: Bosch is Ready to Bring AI to Your (Likely ICE-powered) Vehicle

Webcasts

Semiconductors & ICs

![]() Advantages of Smart Power Distribution Unit Design for Automotive...

Advantages of Smart Power Distribution Unit Design for Automotive...

Unmanned Systems

![]() Quiet, Please: NVH Improvement Opportunities in the Early Design...

Quiet, Please: NVH Improvement Opportunities in the Early Design...

Electronics & Computers

![]() Cooling a New Generation of Aerospace and Defense Embedded...

Cooling a New Generation of Aerospace and Defense Embedded...

Automotive

![]() Battery Abuse Testing: Pushing to Failure

Battery Abuse Testing: Pushing to Failure

Transportation

![]() A FREE Two-Day Event Dedicated to Connected Mobility

A FREE Two-Day Event Dedicated to Connected Mobility