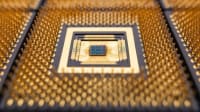

Memory-Based, Structured, Application-Specific Integrated Circuit (ASIC)

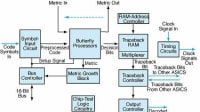

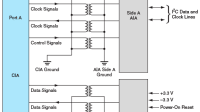

This methodology enables the design of ASICs that include on-chip memory, as well as multiple processing cores, networks-on-chips, and I/O modules.

For air, space, and ground-based systems, there is a clear need for high-performance, lightweight, low-power, highly reliable computing on data-intensive applications. A data-intensive application is one in which there is a very large volume of data, which is often accessed in irregular patterns. Yet, despite the fact that application-specific integrated circuits (ASICs) are becoming more memory-intensive, commodity memory and ASIC design and manufacturing technologies are still on divergent paths.

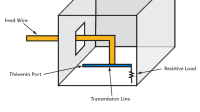

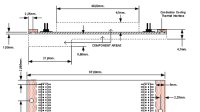

This work explored the use of regular fabrics for lowering the barrier to using commodity memory technology for memory-intensive ASICs. A regular fabric is a system of circuits and design methodologies that best utilizes the simple, regular patterns that can be reliably printed for logic, memory, and analog circuits with a single, compatible, subwavelength lithography setup. In particular, results show that laying out logic circuitry on regular grids that are based on memory array spacing can substantially improve the manufacturability of memory-intensive ASIC designs. Regular fabrics are especially conducive to ebeam lithography, where electron beams transcribe patterns directly to the silicon wafer, without the use of photolithographic masks. Because of this, regular fabrics provide a path for cost-effective, low-volume production by reducing mask cost.

Given the base technology for implementing memory-intensive ASICs that regular fabric provides, a further challenge is giving architects the tools to evaluate tradeoffs and explore the range of possible designs for complex, heterogeneous ASIC designs. Such designs may include many processor cores, interconnection networks, I/O components, and multiple varieties of memory, including 3D stacks or quilts. To address this challenge, both midrange and high-level tools were developed for modeling power, area, and timing in multi- and many-core systems.

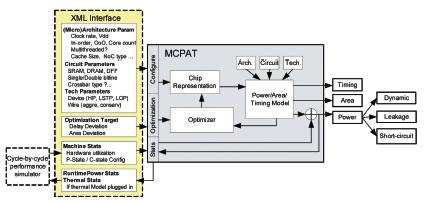

Unlike prior tools, which were tightly integrated with specific performance simulators, McPAT uses an XML interface to decouple the architectural simulator from the power, area, and timing analysis, so that it can be readily used with a variety of simulators. McPAT’s power models account for dynamic power, subthreshold leakage, and gate leakage, as well as short-circuit power, using calculated timing information to determine the interval when both the pull-up and pull-down devices are conducting. It is also the first processor power modeling environment to include both power gating and clock gating, as well as support for P-state and C-state power management schemes. In providing these capabilities, McPAT supports architects in exploring a broad design space for future multicore and many-core systems.

This work was done by Jay Brockman, Peter Kogge, and Michael Niemier of the University of Notre Dame; and Larry Pileggi of Carnegie Mellon University for the Air Force Research Laboratory. For more information, download the Technical Support Package (free white paper) at www.defensetechbriefs.com/tsp under the Electronics/Computers category. AFRL-0140

This Brief includes a Technical Support Package (TSP).

Memory-Based, Structured, Application-Specific Integrated Circuit (ASIC)

(reference AFRL-0140) is currently available for download from the TSP library.

Don't have an account?

Overview

The document titled "Memory-Based Structured Application Specific Integrated Circuit (ASIC) Study" presents a comprehensive analysis of innovative methodologies for designing memory-based ASICs. Authored by researchers from the University of Notre Dame, the report is structured around three major project studies: the evaluation of Structured ASICs (SASICs) using regular fabrics, the development of a midrange framework for modeling complex multicore chips, and the creation of a high-level modeling framework.

The report begins with an introduction to the challenges faced in the design of memory-intensive systems, emphasizing the need for efficient design methodologies that can reduce costs and risks associated with the design cycle. It outlines the approach taken in the study, which includes high-level design space exploration to optimize area, speed, and power.

Key findings highlight the effectiveness of high-level analysis tools in significantly reducing design cycle time and costs. The study demonstrates that system-level tools employing simple heuristic and analytic models, alongside midrange tools that operate with standard architectural simulators, are essential for characterizing a range of designs. The report showcases the PIM Lite chip as a case study, illustrating that implementations using regular patterned "bricks" technology can achieve performance comparable to conventional ASICs while maintaining a design flow that is only slightly more complex.

The document also discusses the benefits of the developed design methodology, which not only aligns with the manufacturing processes of dense memory but also facilitates high-level design space exploration, thereby reducing both front-end and back-end design costs. The findings suggest that further research with more complex reference designs could provide deeper insights into potential savings in design time and costs.

In conclusion, the report emphasizes the importance of patterned ASICs and recommends follow-on work to explore this area further. It serves as a valuable resource for understanding the advancements in ASIC design methodologies and their implications for future technology development. The report is approved for public release and is available for dissemination, contributing to the broader scientific and technical information exchange.

Top Stories

INSIDERDefense

![]() New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

NewsAutomotive

![]() Ford Announces 48-Volt Architecture for Future Electric Truck

Ford Announces 48-Volt Architecture for Future Electric Truck

INSIDERManufacturing & Prototyping

![]() Active Strake System Cuts Cruise Drag, Boosts Flight Efficiency

Active Strake System Cuts Cruise Drag, Boosts Flight Efficiency

ArticlesTransportation

![]() Accelerating Down the Road to Autonomy

Accelerating Down the Road to Autonomy

INSIDERMaterials

![]() How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

Road ReadyTransportation

Webcasts

Electronics & Computers

![]() Cooling a New Generation of Aerospace and Defense Embedded...

Cooling a New Generation of Aerospace and Defense Embedded...

Power

![]() Battery Abuse Testing: Pushing to Failure

Battery Abuse Testing: Pushing to Failure

Connectivity

![]() A FREE Two-Day Event Dedicated to Connected Mobility

A FREE Two-Day Event Dedicated to Connected Mobility

Automotive

![]() Quiet, Please: NVH Improvement Opportunities in the Early Design Cycle

Quiet, Please: NVH Improvement Opportunities in the Early Design Cycle

Transportation

![]() Advantages of Smart Power Distribution Unit Design for Automotive &...

Advantages of Smart Power Distribution Unit Design for Automotive &...

Aerospace

![]() Sesame Solar's Nanogrid Tech Promises Major Gains in Drone Endurance

Sesame Solar's Nanogrid Tech Promises Major Gains in Drone Endurance