The Dataflow Interchange Format for Designing DSPs

Designs can be ported across software tools, libraries, and embedded processing platforms.

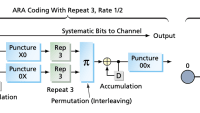

The dataflow interchange format (DIF) is a conceptual framework for helping designers of digital signal-processing (DSP) systems to integrate diverse dataflow models, dataflow techniques, DSP-design software tools, DSP software libraries, and embedded processing platforms. Somewhat more specifically, the DIF is intended to afford a unique combination of capabilities for (1) developing dataflow models and techniques for exploring the complex design spaces for embedded DSP systems; (2) porting DSP designs across various software tools, libraries, and embedded processing platforms; and (3) synthesizing software implementations from high-level, dataflow-based program specifications.

The DIF includes the concepts of a DIF hierarchy and a DIF language. In conventional practice, a sophisticated DSP is usually modeled by means of a hierarchical graph in which the computations associated with certain actors, denoted hierarchical actors, can be specified as nested dataflow graphs. However, the conventional formal dataflow graph definition does not describe such hierarchical nesting. The DIF hierarchy is a means of specifying hierarchical dataflow graphs. In DIF semantics, an actor can represent either an indivisible computation or a hierarchically nested subgraph (denoted a supernode in DIF).

The DIF language is designed as a standard language for specifying DSP oriented dataflow graphs. The DIF language provides a unique set of semantic features to specify graph topologies, hierarchies, and dataflow-related and actor-specific information. DSP applications specified by the DIF language are usually referred to as DIF specifications. The DIF is implemented by means of the DIF package, which is a Java software package that has been (and continues to be) developed along with the DIF language.

Other developments pertaining to the DIF, applications thereof, and related applications include the following:

- A DIF-based methodology has been conceived as a systematic approach for porting DSP designs across design software tools and libraries. The combination of this DIF-based porting methodology and the porting infrastructure provided in the DIF package is intended to enable the efficient migration or development of DSP designs across the tools and libraries. Such migration or development would be equivalent to porting DSP designs across the underlying embedded processing platforms that are supported by the software tools and libraries.

- A DIF-to-C software-synthesis framework provides for automatic generation of C-language software from high-level dataflow specifications of DSP systems. The DIF-to-C framework integrates scheduling, buffering, and code-generation techniques and enables association of dataflow actors with their desired C-language functions. In other words, the DIF-to-C framework offers a useful link between coarse-grain dataflow optimizations and manually optimized libraries, and provides an efficient way to explore the complex range of tradeoffs in the implementation of DSP software.

- A simulation oriented scheduler (SOS) algorithm and software that implements it have been developed to solve major problems encountered in simulating highly multirate systems. The SOS scheduler emphasizes effective, joint minimization of time and memory requirements for simulating critical synchronous dataflow graphs (SDFs). In tests of the SOS software, large reductions in amounts of time and memory needed for simulating large-scale and highly multirate wireless communication systems have been demonstrated.

- A multithreaded simulation scheduler has been developed as a means of reducing simulation time by exploiting multithreaded execution of SDF graphs on multi-core processors. In tests on a commercial dual-core hyper-threading processor comprising four processing units, speedups by factors as large as 3.5 were obtained in simulations of modern wireless communication systems.

This work was done by Chia Jui Hsu of the University of Maryland for the Defense Advanced Research Projects Agency.

This Brief includes a Technical Support Package (TSP).

The Dataflow Interchange Format for Designing DSPs

(reference DARPA-0006) is currently available for download from the TSP library.

Don't have an account?

Overview

The dissertation titled "Dataflow Integration and Simulation Techniques for DSP System Design Tools" by Chia-Jui Hsu, submitted to the University of Maryland in 2007, addresses the complexities involved in designing embedded digital signal processing (DSP) systems. These systems are integral to various communication devices and multimedia applications, such as cellular phones, MP3 players, and digital cameras. The increasing demands for high performance, functionality, low power consumption, cost-effectiveness, and rapid time-to-market have made the design of modern embedded DSP systems increasingly intricate.

Hsu emphasizes the role of electronic design automation (EDA) tools in managing this complexity. These tools assist in various phases of the design process, from physical layout to logical verification. The dissertation proposes a novel framework based on the dataflow interchange format (DIF), which aims to unify different dataflow models, design tools, and DSP libraries. This framework is intended to facilitate the integration of diverse design methodologies and enhance the efficiency of the design process.

The document outlines the challenges faced in the current DSP design landscape, including the need for interoperability among various tools and the ability to simulate and analyze complex systems effectively. Hsu's work focuses on developing techniques that allow for better integration of dataflow models, which can lead to improved simulation capabilities and more efficient design workflows.

The dissertation also discusses the importance of modeling and simulation in the design of DSP systems, highlighting how these processes can help designers visualize and optimize system performance before implementation. By leveraging dataflow models, designers can create more adaptable and scalable systems that meet the evolving requirements of modern applications.

In summary, Hsu's dissertation contributes to the field of DSP system design by proposing a comprehensive framework that addresses the integration and simulation challenges faced by designers. The work aims to enhance the capabilities of EDA tools, ultimately leading to more efficient and effective design processes for embedded DSP systems. This research is significant for both academia and industry, as it provides insights into improving design methodologies and tools in a rapidly advancing technological landscape.

Top Stories

INSIDERManufacturing & Prototyping

![]() How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

NewsAutomotive

![]() Microvision Aquires Luminar, Plans Relationship Restoration, Multi-industry Push

Microvision Aquires Luminar, Plans Relationship Restoration, Multi-industry Push

INSIDERAerospace

![]() A Next Generation Helmet System for Navy Pilots

A Next Generation Helmet System for Navy Pilots

INSIDERDesign

![]() New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

ArticlesAR/AI

![]() CES 2026: Bosch is Ready to Bring AI to Your (Likely ICE-powered) Vehicle

CES 2026: Bosch is Ready to Bring AI to Your (Likely ICE-powered) Vehicle

Road ReadyDesign

Webcasts

Semiconductors & ICs

![]() Advantages of Smart Power Distribution Unit Design for Automotive...

Advantages of Smart Power Distribution Unit Design for Automotive...

Unmanned Systems

![]() Quiet, Please: NVH Improvement Opportunities in the Early Design...

Quiet, Please: NVH Improvement Opportunities in the Early Design...

Electronics & Computers

![]() Cooling a New Generation of Aerospace and Defense Embedded...

Cooling a New Generation of Aerospace and Defense Embedded...

Power

![]() Battery Abuse Testing: Pushing to Failure

Battery Abuse Testing: Pushing to Failure

AR/AI

![]() A FREE Two-Day Event Dedicated to Connected Mobility

A FREE Two-Day Event Dedicated to Connected Mobility