Compact Chip Architecture Provides High-Speed Image Processing

To quickly distinguish friend from foe or make sense of a visual scene, no machine can beat the human eyes and brain — at least not yet. But a better silicon eye has been built with a series of Missile Defense Agency (MDA) Phase I and II Small Business Innovation Research (SBIR) contracts for the development of a chip with a new architecture specifically for highspeed image processing.

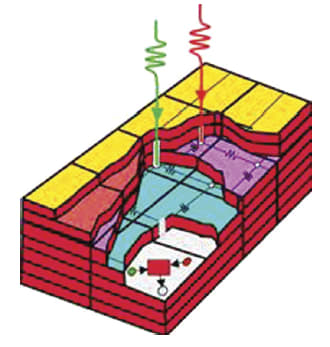

Computational Sensors Corporation (CSC) of Santa Barbara, CA, developed novel architectures and interconnects for massively parallel computing in a compact integrated circuit. This “alternate architecture” involves three-dimensional stacking of integrated circuits beneath a focal plane array, enabling massively parallel image processing at the pixel level.

How It Works

Conventional image processors typically yield data output in the megahertz range, rapidly creating a backlog of information to be sorted and analyzed. To address this backlog and to prepare for high-speed operations — both of which are needed for missile threat discrimination — CSC stacked integrated circuits beneath a two-dimensional detector array. This very-large-scale integration (VLSI) approach enables the chip to perform the image processing onboard the circuitry, and avoid the customary bottleneck at the tail end of the processing stream. The result is a fast, low-power imaging device that boasts a small footprint and light weight.

CSC’s chief innovation is the stacking architecture that eliminates the bottleneck experienced in conventional digital image processing. In turn, the rapid processing capability enhances the ability of an imaging device to perform threat assessment in real time, and to track and identify multiple targets against background clutter. The new architecture was an extension of CSC’s previous MDA-funded thin-film analog processor development, and was designed to pass pixels through the computational process without storing (and therefore slowing) the information provided by the sensor. The resulting capabilities are termed neuromorphic, or comparable to biological or “intelligent” systems, where image processing at the neural level is done on the fly. In this way, the full spectral range of the sensor can be utilized efficiently, with a better signal-to-noise ratio and alias-free operation.

Collectively, CSC’s MDA-related innovations have helped to improve automatic target recognition, target tracking, feature extraction, 3D reconstruction, image classification, and image understanding — parameters that comprise the underpinnings of compact, low-powered, deployable missile defense systems.

Where It Stands

CSC’s image processing products have applications in border security and surveillance, biometric identification, unmanned aerial vehicles (UAVs), ultra-lightweight micro-unmanned aerial vehicles (μUAVs), surface-to-air threat warning for aircraft, mobile military units, medical imaging (CAT and MRI), and possibly nondestructive evaluation (NDE).

Other areas of application are in navigation and guidance markets, as well as automatic inspection and machine vision. CSC sensors could be used on a commercial jetliner, for example, to provide advance warning of a surface-to-air missile attack, an issue that arose in the years following September 11. To combat such a threat, small imaging sensors, placed on the fuselage of a jet and coupled with relevant software, could give warning of an incoming object in time for a pilot to take evasive action. For machine vision/automatic inspection applications in quality control of manufactured goods, the sensors could be used to detect signs of product tampering or contamination.

An application in border security is where infrared cameras are already used to detect movements in the vast areas that constitute much of the U.S. border with Mexico. CSC’s image processing chip, when outfitted with infrared capabilities, could offer better performance to the Border Patrol.

For medical applications, CSC is currently engaged in a study with Lawrence Berkeley National Laboratory and the University of California (UC) at San Francisco Medical School to determine the efficacy of its sensors in the iterative reconstruction of CAT scan and MRI images. In the former case, shorter image processing time can mean faster scans and a lower radiation dose, and in the latter, less time in the noisy and confining MRI apparatus.

More Information

For more information on Computational Sciences Corp.’s 3D stacked integrated circuit technology, visit http://info.hotims.com/ 10970-515.

Rad-Hard Chip Enables Commercial Microprocessors for Space Use

Onboard computers are the primary means of operating satellites that cost millions of dollars to build and launch. Once in orbit, however, these computers are not easily repaired if problems arise. Furthermore, space-deployed hardware cannot tolerate data errors, since ordinary microchip performance degrades considerably outside the Earth’s atmosphere. The traditional method of building spacecraft computers involves the fabrication of very expensive, specialized chips, which result in slow, power-hungry processors.

The Air Force’s Military Satellite Communications program tasked the Air Force Research Laboratory (AFRL) with finding innovative solutions to these challenges. Under an AFRL Small Business Innovation Research (SBIR) contract, Space Micro of San Diego, CA developed a strategy for using commercial microprocessors in space.

How It Works

To address the issues surrounding a commercial microprocessor’s usage in space, Space Micro focused on the dual problems of single-event upsets (a type of radiation-induced data error) and single-event functional interrupt hangups, both of which contribute to the unreliable performance of commercial chips exposed to high-energy cosmic radiation.

To address the issues surrounding a commercial microprocessor’s usage in space, Space Micro focused on the dual problems of single-event upsets (a type of radiation-induced data error) and single-event functional interrupt hangups, both of which contribute to the unreliable performance of commercial chips exposed to high-energy cosmic radiation.

To resolve initial difficulties, the company investigated a way to utilize existing circuitry to perform on-the-fly recalculation (and checking) of computations associated with critical operations. This straightforward approach beats the alternative of running three processors in parallel and voting their outputs. In addition, it uses less hardware and power, because the necessary level of redundancy is easily activated and deactivated as needed.

Space Micro also incorporated a radiation-hardened watchdog chip, which triggers an automatic processor reset if it detects a hang-up in the apparatus. This innovative solution simplifies the architecture by eliminating the need to synchronize multiple processors. The company’s final product consists of a high-performance, fault-tolerant computer known as Proton that employs low-cost, commercially available parts.

Where it Stands

To date, over 50 satellite programs have inquired about this commercially based, inexpensive, low-power approach to space computing systems, with nine various delivery contracts awarded from the Air Force, Missile Defense Agency, NASA, and the Defense Advanced Research Projects Agency (DARPA). Space Micro’s groundbreaking prototype has thus established its legacy as one of AFRL’s most successful SBIR efforts.

Last August, the Proton200k™ computer was selected by the AFRL Space Vehicles Directorate for engineering design and development support for the Autonomous Nanosatellite Guardian Evaluating Local Space (ANGELS) satellite program.

More Information

For more information on Space Micro’s chips, visit http://info.hotims.com/ 10970-516.

Top Stories

INSIDERDefense

![]() New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

NewsAutomotive

![]() Ford Announces 48-Volt Architecture for Future Electric Truck

Ford Announces 48-Volt Architecture for Future Electric Truck

INSIDERManufacturing & Prototyping

![]() Active Strake System Cuts Cruise Drag, Boosts Flight Efficiency

Active Strake System Cuts Cruise Drag, Boosts Flight Efficiency

ArticlesTransportation

![]() Accelerating Down the Road to Autonomy

Accelerating Down the Road to Autonomy

INSIDERMaterials

![]() How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

Road ReadyTransportation

Webcasts

Electronics & Computers

![]() Cooling a New Generation of Aerospace and Defense Embedded...

Cooling a New Generation of Aerospace and Defense Embedded...

Power

![]() Battery Abuse Testing: Pushing to Failure

Battery Abuse Testing: Pushing to Failure

Connectivity

![]() A FREE Two-Day Event Dedicated to Connected Mobility

A FREE Two-Day Event Dedicated to Connected Mobility

Automotive

![]() Quiet, Please: NVH Improvement Opportunities in the Early Design Cycle

Quiet, Please: NVH Improvement Opportunities in the Early Design Cycle

Transportation

![]() Advantages of Smart Power Distribution Unit Design for Automotive &...

Advantages of Smart Power Distribution Unit Design for Automotive &...

Aerospace

![]() Sesame Solar's Nanogrid Tech Promises Major Gains in Drone Endurance

Sesame Solar's Nanogrid Tech Promises Major Gains in Drone Endurance