Small Form Factor Computing in OpenVPX

The new OpenVPX™ (VITA 65) standard helps military system designers build compatible embedded systems by defining “profiles” to which vendors can adhere when designing boards, and system integrators can use to locate available COTS solutions. The market is seeing a proliferation of 6U VPX boards, which have numerous interconnect pins and are able to support many more simultaneous external connections with a single profile. In comparison, 3U VPX boards have fewer interconnect pins available, resulting in a far wider fragmentation of profile support, since vendors can support fewer external connections with a single 3U card profile. That makes it all the more important for designers of small form factor VPX systems to understand how to effectively use OpenVPX profiles.

The Small Form Factor Alternative

As high-speed serial fabrics became increasingly popular in high-performance defense and aerospace embedded applications, the VME Parallel Bus proved insufficient for the needs of higher performance embedded systems. VPX, also known as VITA 46, is the follow-on to the VME Specification for the next generation of high-speed serial interconnects for rugged environments. While advancing the state of the technology, VPX provides backwards compatibility to traditional VMEbus through the use of specialized bridges. Compared to VME and CompactPCI (cPCI) technologies, VPX provides a standards-based COTS solution with multiple signal planes, higher bandwidth, more user I/O pins, built-in ESD-protection, and ease of use in the field. VPX is highly scalable and flexible, featuring a multitude of high-speed pins, high-speed board-to-board communication, and higher power delivery. VPX also introduces two-level maintenance through VITA 48 (VPX-REDI). Another significant advance that VPX provides over VME is the definition of a 3U form factor variant, an alternative that was never successfully provided by VME.

The Small Form Factor Alternative

As demands for reduced Size, Weight and Power (SWaP) have risen, the size and modularity of the 3U form factor has made it the card size of choice for a large number of newer lightweight and compact technology platforms such as UAVs.

3U VPX and VPX-REDI offer an order of magnitude higher bandwidth than older small form factors, with VPX and VPX-REDI delivering 4 to 5 GBps with the defined eight fabric lanes of either PCIe or Serial RapidIO. For high-speed, bandwidth-intensive applications, VPX’s MultiGig RT2 connector supports signaling up to 6.25 Gbps on each differential pair and more with advanced SERDES technologies. 3U VPX can thus take advantage of the high-speed interconnects provided with new multicore platform processors.

Understanding OpenVPX

Due to the vast number of high-speed pins specified by VPX, a wide variety of fabric options are available to system designers. The problem is that a plethora of different implementations from VPX vendors can result in system-wide interoperability issues between VPX modules and chassis. These issues have led the VSO to develop the OpenVPX Systems Specification (VITA 65), a common set of backplanes that define specific system implementations and satisfy the widest range of application needs. OpenVPX™ does not replace VPX; it is a subset of implementations within VPX that addresses Systems Architecture and builds on the VPX Base and Dot specifications, such as 46.1, 46.3, 46.4, 46.7, and 46.11.

OpenVPX employs three key terms that a system designer needs to understand: Planes, Pipes and Profiles. An OpenVPX Plane is an interconnection between boards used to transfer information. The OpenVPX specification defines 5 different planes:

- Utility Plane — common system services or utilities, such as power, sys_reset, geographical addressing, JTAG, etc.

- Management Plane — supervision and management of hardware resources, such as I2C or IPMI;

- Control Plane — application specific software control of the system, typically using Ethernet;

- Data Plane — application specific data traffic, typically at a high-speed. Examples are PCIe and Serial RapidIO (SRIO);

- Expansion Plane — a dedicated high-speed data interconnect between two adjacent boards, typically using PCIe.

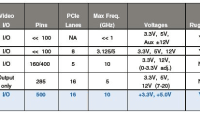

OpenVPX provides a number of different connections from board to board. These are known as Pipes. A pipe is a dedicated differential-pair connection between boards, A pipe does not specify what type of signal is being carried; a pipe is a protocol agnostic transport and can be used for any signal type/protocol and at any speed. The width of a pipe is defined by the number of diff-pair connections:

- UTP (Ultra-Thin Pipe) — 2 diff-pair signals, typically used as one pair in each direction (TX and RX), such as 1000Base-X (SerDes) Ethernet;

- TP (Thin Pipe) — 4 diff-pair signals, such as 1000Base-T Ethernet;

- FP (Fat Pipe) — 8 diff-pair signals, such as 4-lane SRIO or PCIe;

- DFP (Double Fat Pipe) — 16 diff-pair signals;

- QFP (Quad Fat Pipe) — 32 diff-pair signals;

- OFP (Octal Fat Pipe) — 64 diff-pair signals.

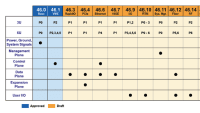

In OpenVPX a Profile is a mapping of physical resources in a system. Each Profile refers to the “view” of the set of connections at a particular place in the OpenVPX system. OpenVPX defines Slot Profiles, Module Profiles, and Backplane Profiles. The Slot Profile defines the pinout. The Module Profile defines the plug-in board, uses a Slot profile for it’s pinout, and defines the protocol and signal speed carried on each pipe.

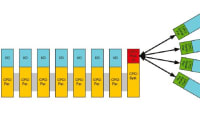

Backplane Profiles

The Backplane Profile puts Slot profiles together and defines the connection between boards. It also defines the maximum backplane signal speed. A systems designer will first choose a backplane topology that will satisfy the computing and I/O needs, based on the requirements of the application. A given topology consists of various backplane profiles which dictate the Payload and, if required, a Switch Profile along with the control, data and expansion plane. Based on the selection of the Backplane Profile, a system designer must then verify that the combination of the Slot Profile and Module Profile will satisfy the system requirements. The Payload and Switch Profile will define the pin allocation. Both the Slot and Backplane Profile are protocol agnostic. The designer must then select the appropriate Module Profile to ascertain the composition of high-speed serial fabrics required.

A Backplane Profile puts number and type of boards on a backplane, and wires them up with an interconnect topology. The Backplane Profile defines the mechanical pitch and most importantly, the slot profile for all boards. Finally, the Backplane Profile defines the maximum signal speed (Gbaud) carried on the pipes, but not the protocol.

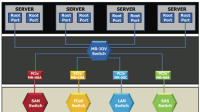

There are three backplane profiles currently defined: distributed switching, centralized switching and hybrid.

A distributed switching topology is one in which the data plane pipes are connected directly between payload slots or between payload and peripheral slots. This is preferable in smaller, SWAP-constrained systems. A control plane switch may or may not be included in this profile.

A centralized switching backplane topology is one in which there is one or more central data plane switches. In most cases there are also switches for the control plane (usually the same switching module is used for both). The only exceptions are two centralized switch profiles that have a single payload module and several peripheral modules in a chassis and all the peripheral modules are connected to the payload module over the data plane.

A hybrid profile combines both VPX and VME slots in a single chassis. It may or may not have a central data plane switch. This profile is useful when there are legacy system requirements that require one or more VME slots.

Slot Profiles vs Module Profiles

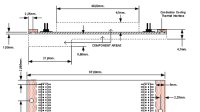

A Slot Profile defines the backplane pinout of a VPX slot. They also assign pipes to specific connector pins. VPX boards will map their backplane pinout to match a specific Slot Profile. Slot Profiles do not care what protocol or speed is carried on the pipes.

A Module Profile, on the other hand, references a Slot Profile for its pinout, and then defines the Protocol and signal speed supported. OpenVPX boards must comply to a Module Profile. The final number of the profile suffix (For example,“n”inMOD6-PAY-4F1QU2T-12.2.1-n) defines the protocol and speed combinations on the pipes.

The module profiles currently defined are payload, peripheral, switch, bridge and storage.

A payload module provides hardware processing and/or I/O resources required to satisfy the needs of the top-level application. For example, a Payload Module might be an embedded processor or an I/O controller Module.

A peripheral module is subservient to a payload module’s Peripheral slots and communicates with its nearest neighbor payload slots over PCIe. Examples include mezzanine card carriers, I/O expansion cards and processing off-load engines (such as GPGPUs).

A switch module minimally serves the function of aggregating Channels from other Plug-In Modules. This module terminates the aggregated Channels and provides the necessary switch fabric(s) to transfer data frames between two plug-in modules.

A bridge module is used to communicate between modules that support different protocols, for example, between two different VPX data plane fabric protocols or between VPX and VME.

A storage module provides the function of a disk drive. An example is a SATA carrier.

Designing an OpenVPX System

Knowing how to use OpenVPX Profiles to define a new system and identify available boards from multiple vendors helps to speed system configuration by maximizing interoperability. The basic steps in designing an OpenVPX system are as follows:

Step 1: Choose the size (3U or 6U)and number of slots based on proposed functionality/payload.

Step 2: Pick the Data Plane Connection Architecture. in a centralized Switching Architecture which is ideal for flexibility and expandability, all boards connect to one or more central switches. In a distributed Architecture, boards are connected directly to other boards, resulting in a fixed connection relationship between boards and no central switch. (NOTE: The Control Plane is almost always a Central Switch architecture.)

Step 3: Identify the closest matching Backplane Profile in terms of number of slots, connection architecture, etc. (NOTE: it’s easiest to make minor changes to an already established profile.)

Step 4: Find the Processing and Switching Cards to match the Backplane Profile, ensure the Module Profiles match slots in the backplane, and match each other’s connection profile, protocols and speeds.

As the demand for high performance, rugged, small form factor embedded computing increases, it will become all the more critical for system designers to familiarize themselves with the OpenVPX profiles system. The resulting increase in interoperability will bring new advanced systems to market, and speed the deployment of state-of-the art processing solutions to the warfighter.

This article was written by Steve Edwards, Chairman, VITA 65 Working Group (Fountain Hills, AZ). For more information, contact Mr. Edwards at

Top Stories

NewsRF & Microwave Electronics

![]() Microvision Aquires Luminar, Plans Relationship Restoration, Multi-industry Push

Microvision Aquires Luminar, Plans Relationship Restoration, Multi-industry Push

INSIDERAerospace

![]() A Next Generation Helmet System for Navy Pilots

A Next Generation Helmet System for Navy Pilots

INSIDERDesign

![]() New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

New Raytheon and Lockheed Martin Agreements Expand Missile Defense Production

INSIDERMaterials

![]() How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

How Airbus is Using w-DED to 3D Print Larger Titanium Airplane Parts

NewsPower

![]() Ford Announces 48-Volt Architecture for Future Electric Truck

Ford Announces 48-Volt Architecture for Future Electric Truck

ArticlesAR/AI

Webcasts

Electronics & Computers

![]() Cooling a New Generation of Aerospace and Defense Embedded...

Cooling a New Generation of Aerospace and Defense Embedded...

Automotive

![]() Battery Abuse Testing: Pushing to Failure

Battery Abuse Testing: Pushing to Failure

Power

![]() A FREE Two-Day Event Dedicated to Connected Mobility

A FREE Two-Day Event Dedicated to Connected Mobility

Unmanned Systems

![]() Quiet, Please: NVH Improvement Opportunities in the Early Design Cycle

Quiet, Please: NVH Improvement Opportunities in the Early Design Cycle

Automotive

![]() Advantages of Smart Power Distribution Unit Design for Automotive &...

Advantages of Smart Power Distribution Unit Design for Automotive &...

Energy

![]() Sesame Solar's Nanogrid Tech Promises Major Gains in Drone Endurance

Sesame Solar's Nanogrid Tech Promises Major Gains in Drone Endurance